## Three Dimensionally Interconnected Silicon Nanomembranes for Optical Phased Array (OPA) and Optical True Time Delay (TTD) Applications

## **Contract Monitor:**

Dr. GernotPomrenke

# **Contract No.:** AFOSR MURI GRANT FA9550-08-1-0394

## Lead Principal Investigator:

Ray T. Chen The University of Texas at Austin MURI Website: http://muri.engr.utexas.edu/

# **Table of Contents**

| Section | Theme                                                                | Page Number |  |  |  |

|---------|----------------------------------------------------------------------|-------------|--|--|--|

| А       | Summary of Accomplishments                                           | 3           |  |  |  |

| 1.0     | 1x12 Unequally-spaced Waveguide Array for Actively-tuned Optical     | 5           |  |  |  |

| 1.0     | Phased Array on a Silicon Nanomembrane                               | 5           |  |  |  |

| 2.0     | Ultra-compact and Fabrication-Tolerant Integrated Polarization       | 11          |  |  |  |

|         | Splitter                                                             | ••          |  |  |  |

| 3.0     | Ultralow-loss polycrystalline silicon waveguides and high uniformity | 17          |  |  |  |

|         | 1x12 MMI fanout for 3D photonic integration                          |             |  |  |  |

| 4.0     | Vertically Integrated Double-layer On-chip Silicon Membranes for 1-  | 26          |  |  |  |

|         | to-12 Waveguide Fanouts                                              | 20          |  |  |  |

| 5.0     | Double-layer Photonic devices Based on Transfer Printing of Silicon  | 34          |  |  |  |

|         | Nanomembrane for Three-dimensional Photonics                         |             |  |  |  |

| 6.0     | CMOS Compatible High Efficiency Subwavelength Grating Couplers       | 37          |  |  |  |

| 0.0     | for Silicon Integrated Photonics                                     |             |  |  |  |

| 7.0     | On-chip spot size converter for fiber to chip coupling               | 46          |  |  |  |

|         | Coupling loss minimization of slow light slotted                     |             |  |  |  |

| 8.0     | photonic crystal waveguides using mode                               | 53          |  |  |  |

|         | matching with continuous group index perturbation                    |             |  |  |  |

| 9.0     | Silicon Nanomembrane Based Photonic Crystal Waveguide Array for      | 61          |  |  |  |

|         | Wavelength-Tunable True-Time-Delay Lines                             | 01          |  |  |  |

| 10.0    | Passive and active slow light photonic crystal structures            | 68          |  |  |  |

| 11.0    | Large area single crystalline silicon nanomembrane fabrication for   |             |  |  |  |

|         | MMI structure                                                        |             |  |  |  |

| 12.0    | Lithography for silicon nanomembranes                                | 78          |  |  |  |

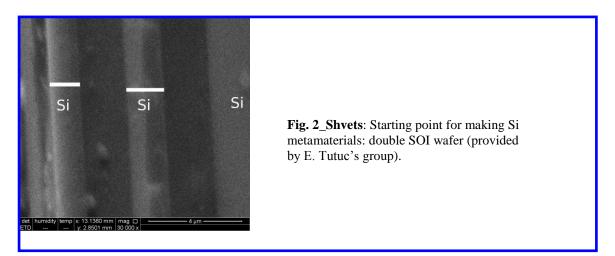

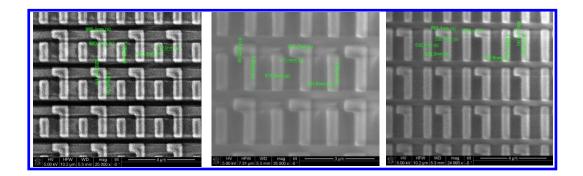

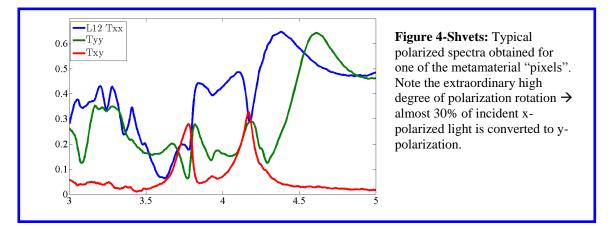

| 13.0    | High-Q Resonances From Si-Nanomembrane Based Metamaterials           | 81          |  |  |  |

| 14.0    | Conclusion                                                           | 90          |  |  |  |

| 15.0    | Major Publications in this period                                    | 91          |  |  |  |

# Summary of Accomplishments

- We present an experimental demonstration of an optical phased array implementation on silicon nanomembrane. The integrated on-chip array configuration is non-uniform and avoids grating lobes inside the field of view during beam steering while allowing the waveguide separation to be large enough to prevent optical coupling. A 1x12 multimode interference beam splitter uniformly excites the arrayed waveguides. Individually controllable microheaters modulate the optical phase in the arrayed waveguides. A beam steering angle of 10.2° in a silicon planar guide equivalent to an effective steering angle of 31.9° in air is demonstrated at 1.55µm.

- 2. Design and fabrication of a 2x2 two-mode interference (TMI) coupler based on-chip polarization splitter is presented. By changing the angle between the access waveguides, one can tune the effective TMI length for the mode with less optical confinement (Transverse Magnetic, TM) to coincide with the target TMI length for a desired transmission of the mode with higher optical confinement (Transverse Electric, TE). The fabricated 0.94µm long 2x2 TMI splits the input power into TM (bar) and TE (cross) outputs with splitting ratio over 15dB over 50nm bandwidth. Fabrication tolerance analysis shows that the device is tolerant to fabrication errors as large as 60nm.

- 3. We have investigated the feasibility of multimode polysilicon waveguides to demonstrate the suitability of polysilicon as a candidate for multilayer photonic applications. Solid Phase Crystallization (SPC) with a maximum temperature of 1000°C is used to create polysilicon on thermally grown SiO2. We then measure the propagation losses for various waveguide widths on both polysilicon and crystalline silicon platforms. We find that as the width increases for polysilicon waveguides, the propagation loss decreases similar to crystalline silicon waveguides. At a waveguide width of 10μm, polysilicon and crystalline silicon waveguides have propagation losses of 0.56dB/cm and 0.31 dB/cm, respectively, indicating there is little bulk absorption from the polysilicon and is the lowest propagation loss for polysilicon demonstrated to date. In addition, the first 1x12 polysilicon MMI is demonstrated with a low insertion loss of -1.29dB and a high uniformity of 1.07dB. These results vindicate the use of polysilicon waveguides of varying widths in photonic integrated circuits.

- 4. We present an on-chip vertically integrated three-dimensional photonic integrated circuit. Double-layer 1x12 multimode interference (MMI) couplers are fabricated on silicon membranes using double-bonded silicon-on-insulator wafers. The input light is transverse electric polarized operating at 1550nm. The top layer MMI coupler has an excess loss of 0.48dB and uniformity within 1.1dB. The bottom layer MMI coupler has an excess loss of 2.9dB and uniformity within 1.7dB.

- 5. We propose a novel platform for three dimensional photonics. A double layer 1x12 multimode interference coupler is fabricated based on transfer printing of silicon nanomembrane. Optical characterizations confirm low insertion loss and uniform outputs.

- 6. We demonstrate a single-step through-etched, grating couplers based on subwavelength nanostructures. The grating consists of arrays of 80 nm x 343 nm rectangular air holes, which can be patterned in a single lithography/etch. A peak coupling efficiency of 59 % at 1551.6 nm and a 3 dB bandwidth of 60 nm are achieved utilizing the silicon-on-insulator platform with a 1 μm thick buried-oxide layer for TE (transverse electric) mode. The performance is comparable to gratings requiring much more complicated fabrication processes.

- 7. We have shown the design and experimental results as a proof of concept for a low loss and broadband on-chip spot size converter that can significantly reduce the insertion loss between a optical fiber and a silicon photonic chip. The spot size converter demonstrated has a 5dB coupling loss. This structure will create a better interface between a fiber and a silicon photonic chip, and help drive the implementation of silicon photonics technology in areas such as optical communications and sensors.

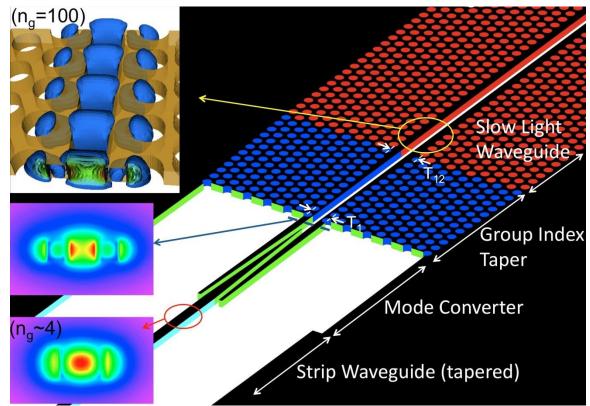

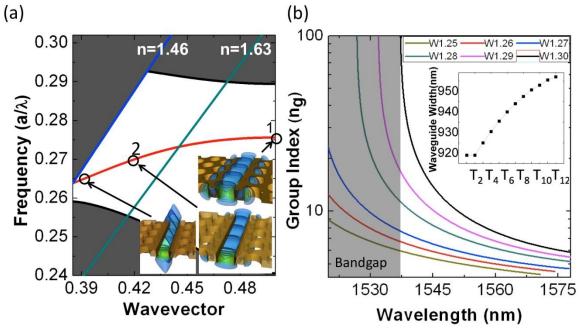

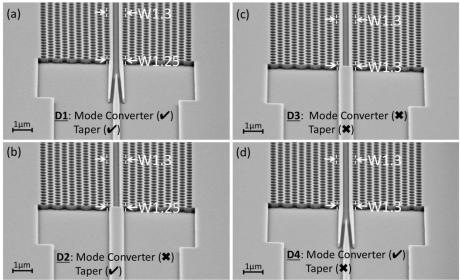

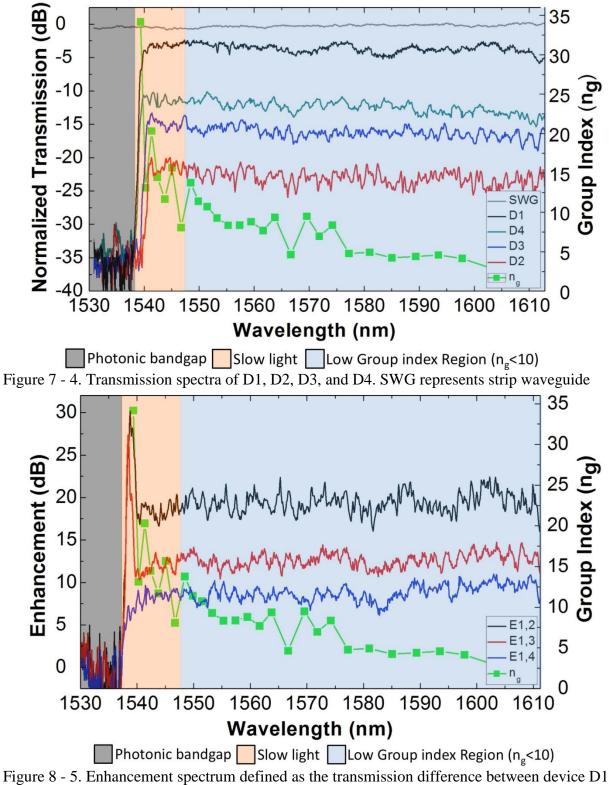

- 8. We experimentally demonstrate highly efficient coupling into a slow light slotted photonic crystal waveguide. With optical mode converters and group index tapers that provide good optical mode matching and impedance matching, a nearly flat transmission over the entire guided mode spectrum of 68.8nm range with 2.4dB minimum insertion loss is demonstrated. Measurements also show up to 20dB baseline enhancement and 30dB enhancement in the slow light region, indicating that it is possible to design highly efficient and compact devices that benefit from the slow light enhancement without increasing the coupling loss.

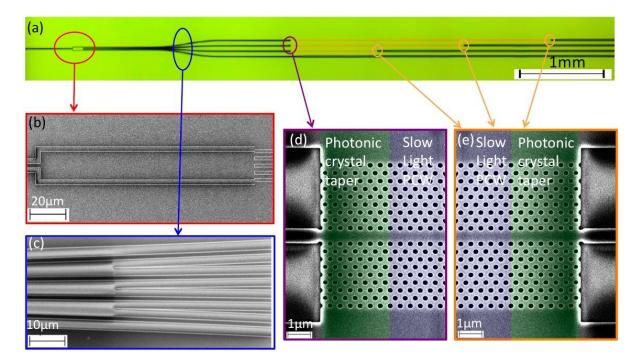

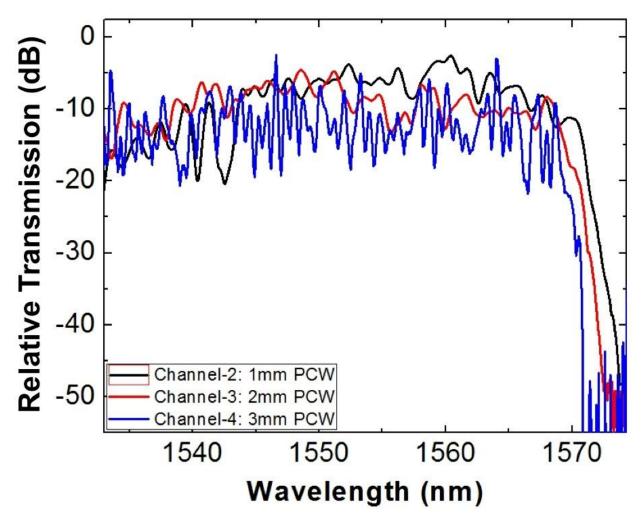

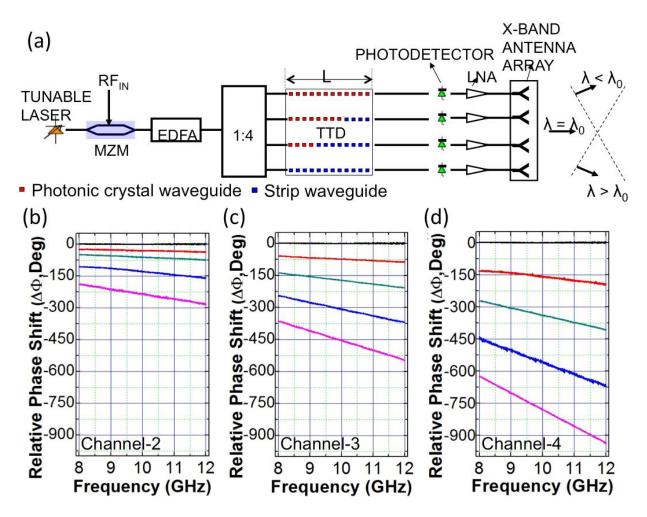

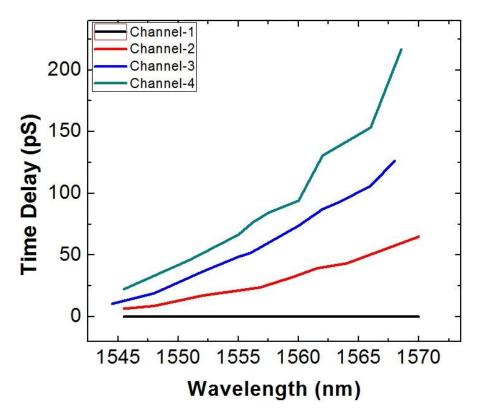

- 9. We demonstrate a four-channel on-chip true-time-delay module based on a photonic crystal waveguide array. Using the photonic crystal taper to minimize the coupling loss, the delay lines with 1~3mm long photonic crystal waveguides can operate up to a group index ng~23 without significant loss. The large group velocity dispersion enables continuous and wavelength-tunable time delays. Measurements show a highly linear phase-frequency relation, highest time delay up to 216.7ps, and large tuning ranges of 58.28ps, 115.74ps, and 194.16ps for 1~3mm delay lines. The chip-scale true-time-delay module occupies only 0.18mm2 area and can provide ±44.38° steering for an X-band phased-array-antenna.

# 1.0 1x12 Unequally-spaced Waveguide Array for Actively-tuned Optical Phased Array on a Silicon Nanomembrane

Traditionally, optical beam steering has been achieved through mechanically controlled MEMS system [1] and liquid crystal (LC) based optical phased arrays (OPAs) [2-4]. While mechanical beam steering provides high steering efficiency and relatively large scanning angles, high precision rotating stages are required, which increase the device complexity and are not fast enough for high speed applications. LC OPAs are capable of beam steering without expensive and complex mechanical systems but suffer from low steering speed (~10ms) and limited steering angle (<10°) [4]. Also, increased steering angle causes degradation of the side-lobe level (SLL) and prohibitively coarse angular resolution [5].OPAs can also be implemented using waveguide arrays. A 2-element waveguide array on GaAs with GHz steering speed was demonstrated with a maximum steering angle of ~6° [6]. A thermo-optically controlled waveguide array fabricated on silicon-on-insulator (SOI) demonstrated a steering angle of  $2.3^\circ$  at a wavelength of 1550 nm [7].

For uniform OPAs capable of large angle beam steering, an inter-element spacing of about one-half the operating wavelength is required whichwould result in strong coupling between adjacent waveguides in the array. In order to overcome this trade-off between the maximum steering angle and waveguide spacing for linear uniform arrays, we proposed a non-uniform array consisting of uniform sub-arrays with non-overlapping grating lobes [5]. Also, compared to a uniform array with half-wavelength spacing, the larger total aperture of such an array results in narrower beam width in the far field, which is advantageous for scanning applications [5]. In this letter we report the implementation of a non-uniform optical array for large angle beam steering.

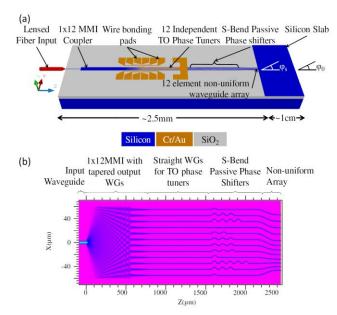

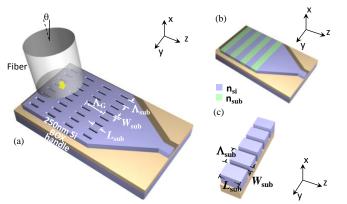

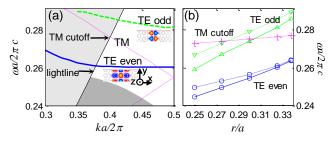

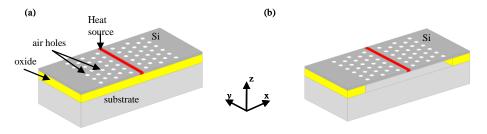

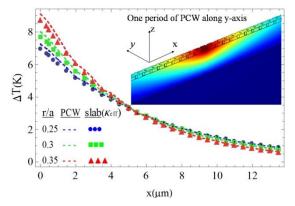

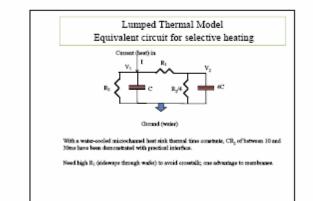

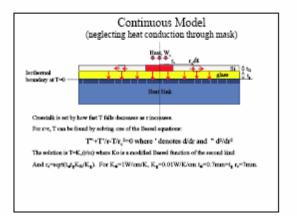

A schematic of the OPA device on SOI is shown in Figure 1(a), showing both photonic and electronic layers vertically separated by a layer of silicon dioxide for optical isolation. The beam propagation simulation of the photonic circuitry of Figure 1(a) at  $\lambda$ =1.55µmis shown in Figure 1(b). The optical input power is uniformly divided into 12 waveguides using a 1x12 multimodeinterference (MMI) beam splitter, which has a width and length of 60µm and 553.4µm, respectively. The input and output access waveguides' widths are 2.6µm, which has been optimized for high MMI performance [8]. The MMI output access waveguides' widths are adiabatically tapered down to 500nm over 250µm length using a linear taper for single mode operation. Previously, we reported that this MMI coupler has an insertion loss of 1.13dB, and uniformity fluctuation within 0.72dB [9]. The input light is transverse-electrically (TE) polarized that provides higher optical mode confinement compared to the transverse-magnetic (TM) polarization for 500nm x230nm single mode silicon waveguides [Fig. 2(a)]. Also, due to the large index discontinuity at the top and bottom waveguide faces, the TM mode profile has larger vertical spread that reaches the micro-heaters and result in high propagation loss with a 1µm top cladding of SiO<sub>2</sub>.

FIG 1-1.(a) A schematic of the silicon waveguide based optical phased array. (b) Beam propagation simulation of the photonic circuit.

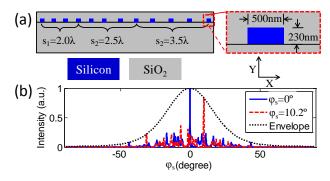

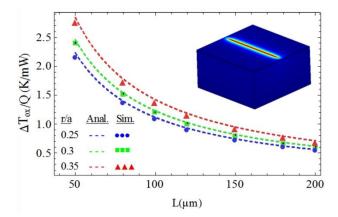

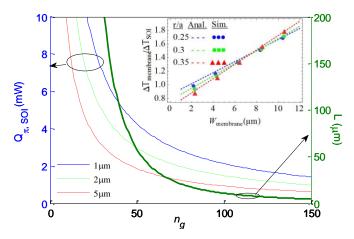

There are 12 independently addressed 800nm wide and 500µm long thermo-optic (TO) phase modulators, as depicted in Fig. 1(a), to provide continuous phase tuning needed for beam steering. Independent phase shiftersenable us to reset with modulo  $2\pi$  phase shifts ( $2m\pi + \Delta\theta_n = \Delta\theta_n$ , where *m* is a positive integer and  $\Delta\theta_n$  is the phase shift of the *n*<sup>th</sup> element) [10]. The following passive s-bend phase shifters [Figure 1(b)] compensate for the quadratic MMI beam splitter output phase profile [11] and change the separation of the uniform MMI outputs to that of the non-uniform array. This phase compensation allows the output beam to be steered at 0° when no heat is applied to the 12 phase shifters. The waveguides are then arranged in a non-uniform 12-element array, consisting of 3 four-element uniform sub-arrays, as shown in Figure 2(a). The spacing of each*i*<sup>th</sup> sub-arrays*i* is chosen such that there is no overlap of its far-field grating lobes with those of the other sub-arrays [5]. The smallest inter-element spacing is 3.1µm and the total array size is*A*=46.5µm.

FIG 1-2. (a) 12-element non-uniform array design with 3 sub-arrays of single-mode silicon waveguides embedded in silicon dioxide, with dimensions of a single waveguide shown in the inset. (b) Theoretical far-field pattern for a non-steered and a steeredbeam inside the planar guide. The envelope is the far field pattern of a single silicon waveguide embedded in silicon dioxide.

The OPA output waveguides are terminated at a 1cm long silicon planar guide, in which the interference of the light from the 12-channel array results in beam steering at the far field zone. The steering angle is observed along the exit side of the planar guide at the chip edge [Figure 1(a)]. For the far field condition to be satisfied,  $n_{eff} A^2/(D\lambda) < 1$  is required [12], where A is the aperture size of the OPA,  $\lambda$  is the

operating wavelength, and D is the distance of the observation point from the array (here the length of the silicon planar guide), and  $n_{eff}$  is the effective refractive index of propagation inside the silicon slab. Similar to the uniform array, the non-uniform array is linearly phased, that is for any  $n^{th}$  array element,  $\gamma_n / |\overline{d_n}| = r$ , where  $\gamma_n$  is the phase applied to the  $n^{th}$  element,  $\overline{d_n}$  is the position vector of the  $n^{th}$  element, and r is a constant. The steering angle inside the silicon planar guide is given as  $\varphi_s = \arcsin\left(\omega_{\sqrt{\mu\varepsilon_{eff}}} / r\right)$

. Note that as the beam reaches the end of the slab and enters free space, its direction is governed by Snell's Law. The theoretical far field patterns for steered and non-steered beams are shown in Figure 2(b).

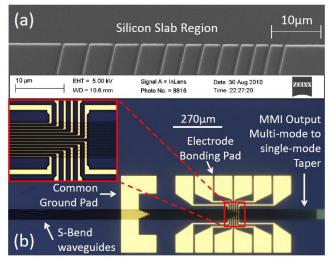

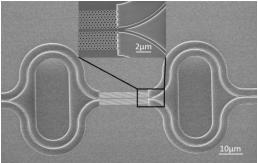

We used SOI from SOITEC with  $3\mu$ m buried oxide (BOX) and 250nm top silicon layer, which is thermally oxidized to create an oxide etch mask, leaving a final silicon thickness of 230nm. Electron beam lithography and reactive ion etching is used to pattern this layer to form the photonic circuitry. A scanning electron microscope (SEM) picture of the interface between the unequally spaced OPA and silicon nanomembraneplanar guide is shown in Figure 3(a). Using the Plasmatherm 790, a 1µm thick film of plasma-enhanced chemical vapor deposition (PECVD) silicon dioxide ( $325^{\circ}$ C, 80W, 400mTorr, 42sccm N<sub>2</sub>O, 21sccm SiH<sub>4</sub>) was deposited as top cladding, which is sufficient to isolate the TE guided modes from the electrodes to prevent high optical loss. Metal heaters are patterned over the waveguides by e-beam lithography and thermal evaporation and liftoff of 150nm of Cr/Au [10/140] film. An optical microscope picture of the heaters aligned over the output waveguides and 12 bonding pads is shown in Figure 3(b).

FIG 1-3. (a) Tilted SEM view of the unequally spaced OPA output and silicon nanomembraneplanar guide. (b) Optical microscope picture of the 12 thermo-optic heaters with bonding pads.

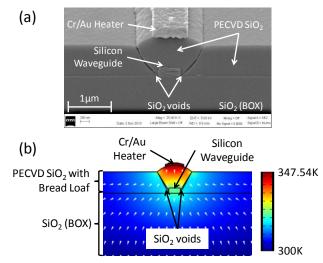

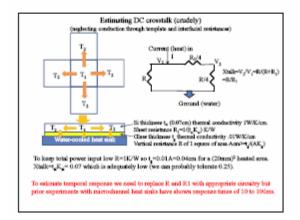

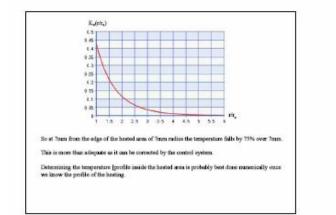

We engineered the "bread loafing" effect in which self-aligned voids are formed during PECVD oxide deposition, and are shown in Figure 4(a). COMSOL Multiphysics simulations in Figure 4(b) indicate the effectiveness of these voids in directing the generated heat toward the silicon waveguides by reducing lateral heat transfer, and therefore reducing the required power for phase shifting. To accurately characterize the phase perturbations of the thermo-optical modulators, we fabricated Mach-Zehnder (MZ) modulators alongside the OPA devices with dimensions identical to the OPA with regard to waveguide and heater geometry. We experimentally confirmed a switching power of  $P_{\pi}$ =12.4mW along with a switching time of 9.8µs which corresponds to a steering speed of 100kHz.

FIG 1-4. (a) SEM cross section of a heater over its waveguide. (b) COMSOL Multiphysics simulation of the thermal profile of the microheater and waveguide cross section with bread loafing of the oxide.

TE polarized light at 1550nm from a polarization maintaining lensed fiber (PMF) with a  $2.5\mu$ m output mode diameter was coupled into the input waveguide. An infrared (IR) camera connected to a variable objective lens captured the top-down far field image at the end of the silicon planar guide.

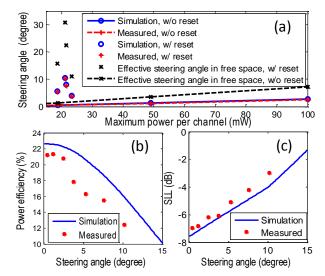

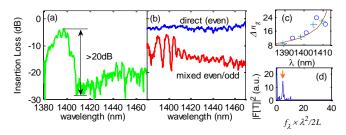

For active beam steering, we first set the input voltages to thermo-optically modulate the array phases in such a way that the electrical power applied to the micro-heaters, and therefore the applied phase shift of the corresponding array element, is linearly proportional to the distance of the element from the origin. Figure 5(a) demonstrates the measured beam steering angle at the edge of the silicon planar guide, along with the theoretical steering angles as a function of the electrical power to the outermost array element, which needs the largest phase shift. The required electrical input power is calculated using the phase shift data from the MZ test. As shown in Figure 5(a), when the steering angle increases, the power required for beam steering without reset becomes prohibitively large for our voltage source and limits us to a steering angle of 2.5° inside the silicon planar guide. Figure 5(a) also shows beam steering angles achieved with reset by applying modulo  $2\pi$  phase shifts to the independently controlled electrodes. We were able to steer the beam at 10.2° inside the silicon planar guide equivalent to an effective angle of 31.9° in air as predicted by Snell's Law, with SLL better than -3dB, while limiting the maximum power per channel to less than P<sub>2π</sub>=24.8mW.

FIG 1-5.Far field characterization, (a) simulated and measured steering angle versus maximum power per channel. Effective steering angles in free space are determined from measurement data. (b) Power efficiency versus steering angle, (c) side-lobe-level versus steering angle.

Using a similar technique as [12], the OPA far field is observed and is used to characterize its output performance. Figures 5(b) and 5(c) demonstrate the OPA performance characterization based on the power efficiency and SLL as functions of the measured steering angle, respectively. The power efficiency is calculated by integrating the intensity over the angle interval that constitutes the main lobe (within  $1/e^2$  of the maximum beam intensity). The resulting is then normalized to intensity integrated over  $-90^0$  to  $+90^0$ . From the simulations, we expect -4dB SLL at 10.2°. The degradation in the performance is due to the variation in P<sub>2π</sub> of the micro-heaters, which results in increasing inaccuracies in the applied phase shift as the number of resets increases at larger steering angles. Using the effective index of the planar guide,  $n_{eff} = 2.9$ , we determine that the 10.2° steering in the planar guide corresponds to a steering angle in free space of 31.9°.

In summary, using a silicon nanomembrane based unequally spaced 1x12 waveguide array for actively tuned OPA that relaxes the strict waveguide spacing requirement for large angle beam steering, we have demonstrated a steering angle in free space of  $31.9^{\circ}$  at  $1.55\mu$ m wavelength. Our optical beam steering system is fabricated on SOI using CMOS compatible processes. Phase modulation is achieved thermo-optically via the use of thin-film metal heaters that are independently controlled. We have demonstrated that low-power optical beam steering is possible by applying modulo  $2\pi$  phase shifts to the independently controlled electrodes. The steering speed is determined by the TO phase shifting mechanism and is 100KHz using the TO effect, which is 2 orders of magnitude larger than LC OPAs.

This research is supported by the Multi-disciplinary University Research Initiative (MURI) program through the AFOSR, contract # FA 9550-08-1-0394.

#### References

- [1-1] Y. Pétremand, P.-A. Clerc, M. Epitaux, R. Hauffe, W. Noell, and N. F. de Rooij, Proc. SPIE 6715, 671502 (2007).

- [1-2] P.F. McManamon, T. A. Dorschner, D. L. Corkum, L. J. Friedman, D. S. Hobbs, M. Holz, S. Liberman, H. Q. Nguyen, D. P. Resler, R. C. Sharp, and E. A Watson, Proc. IEEE 84(2), 268–298 (1996).

- [1-3] X. Wang, B. Wang, J. Pouch, F. Miranda, J. E. Anderson, and P. J. Bos, Opt. Eng. 43, 2769-2774 (2004).

- [1-4] X. Wang X., B. Wang B., P. Bos, P. F. McManamon, J. J. Pouch, F. A. Miranda, and J. E. Anderson, J. Appl. Phys. 98, 073101 (2005).

- [1-5] A. Hosseini, D. N. Kwong, Y. Zhao, Y. –S Chen, F. Crnogorac, R. F. W. Pease, and R. T. Chen, IEEE J. Sel. Topics Quant. elect. 15(5), 1439-1446 (2009).

- [1-6] M. Jarrahi, R. F. W. Pease, D. A. B. Miller, and T. H. Lee, J. Vac. Sci. Technol. B 26, 2124-2126 (2008).

- [1-7] K. V. Acoleyen, W. Bogaerts, J. Jágerská, N. Le Thomas, R. Houdré, and R. Baets, Opt. Lett. 34, 1477-1479 (2009).

- [1-8] A. Hosseini, H. Subbaraman, D. N. Kwong, Y. Zhang, and R. T. Chen, Opt. Lett. 35, 2864-2866 (2010).

- [1-9] D. N. Kwong, Y. Zhang, A. Hosseini, Y. Liu, and R. T. Chen, IET Electronics Letters, 46(18), 1281-1283, (2010).

- [1-10] I. M. Soganci, T. Tanemura, K. A.Williams, N. Calabretta, T. de Vries, E. Smalbrugge, M. K. Smit, H. Dorren, and Y. Nakano, IEEE Photonics Technology Letters, 22(3), 143-145 (2010).

- [1-11] A. Hosseini, D. N. Kwong, Ch.-Y. Lin, B. S. Lee, and R. T. Chen, IEEE J. Sel. Topics Quant. elect. 16(1), 61-69 (2010).

- [1-12] A. Hosseini, D. N. Kwong, Y. Zhang, A. Alu, and R. T. Chen, Appl. Opt. 50(13), 1822-1826 (2011).

#### 2.0 Ultra-compact and Fabrication-Tolerant Integrated Polarization Splitter

On-chip polarization splitters (PSs) are key components of integrated photonic circuits that consist of polarization-dependent devices [1]. Interference-based passive PSs provide low-loss operation and high polarization splitting ratio (SR), and can be designed for single etch step fabrication [2]. The interference-based PSs that have been demonstrated thus far, utilize either directional couplers [2][3], or multimode-interference couplers (MMIs) [4][5].

Symmetric directional coupler based PSs can be shortened ( $\sim 100\mu$ m) by reducing the gap between the coupled waveguides [3]. However, this also degrades the device fabrication tolerance, and potentially lowers its SR.Non-symmetric directional couplers can be designed to allow only one of the modes (TE or TM) to couple out of the input waveguide. Thedevice fabrication tolerance can be improved by waveguide tapering[2]. However, this technique assumes linear design conditions that require relatively large gaps and thus, due to long coupling lengths, the resulting devices are  $\sim 1500\mu$ m long [2].

In MMI based PSs, TM and TE polarizations can be split into different bar or cross states using the difference in their self-imaging beat-lengths,  $L_{\pi} = \pi/(\beta_0 - \beta_1)$ , where  $\beta_n$  is the n<sup>th</sup> mode propagation constant supported by the multimode section [6]. In order to avoid long MMIs due to small beat-length differences of TM and TE polarizations, the required MMI length can be shortened by use of four-mode interference couplers [4], and further by use of two-mode interference (TMI) couplers [5].

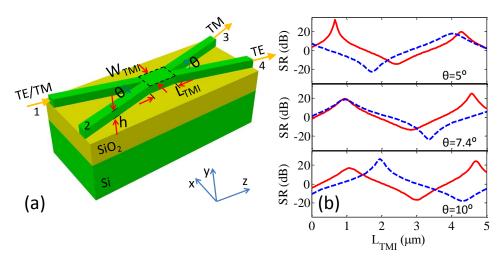

Fig. 2-1.(a) A schematic of the polarization splitter device. (b) Variations of P4/P3 and P3/P4 for input TE (solid red line) and TM (dashed blue line) polarized light, respectively, atdifferent  $\theta$  values, for  $W_{TMT}$ =900nm and h=230nm at  $\lambda$ =1550nm.

In order for a TMI to function as a polarization splitter, the TMI length  $(L_{TMI})$  is chosen to be simultaneously equal to an odd (even) multiple of  $L_{\pi}$  for the TE polarization  $(L_{\pi}^{TE})$  and an even (odd) multiple of  $L_{\pi}$  for the TM polarization  $(L_{\pi}^{TM})$ . A PS device on silicon-on-insulator (SOI)with  $L_{TMI}$  (not including the access waveguides) as short as8.8µm has been demonstrated [5]. However, the resulting TMI is still several beat-lengths long. Since the fabrication tolerance and optical bandwidth of MMI devices are inversely proportional to their length [7], it is beneficial to reduce the TMI length to its absolute minimum, one beat-length. In this letter, we report the design and fabrication of a one-beat-length long TMI based PS.

A schematic of the proposed TMI based PS on SOI is shown in Fig. 1(a). The thicknesses of the oxide and top silicon layers (*h*) are 3µm and 230nm, respectively. A TMI width 800nm< $W_{TMI}$ <950nm supports only two TE and two TM modes, suitable for TMI operation [8]. The input /output access waveguide width is  $W_w = W_{TMI}/2$ . For a TMI, the output power at port 3 and 4 normalized to input power at port 1 (port 2 is idle) is given as  $P_3/P_1 = \sin^2(\pi L_{TMI}/2L_{\pi} + \varphi)$  and  $P_4/P_1 = \cos^2(\pi L_{TMI}/2L_{\pi} + \varphi)$ , where, the phase term,  $\varphi$ , is determined by the coupling between the two access waveguides at the input and output. Assuming fixed *h*, only  $W_{TMI}$  and  $L_{TMI}$  have been thus far considered as the design parameters while the effect of  $\varphi$ on the device operation has been ignored.

Fig. 2-2. FDTD Propagation field profiles for TE (Ex) and TM (Hx) input polarizations for  $\theta$ =7.4°,  $L_{TMI}$ =940nm,  $W_{TMI}$ =900nm and h=230nm at  $\lambda$ =1550nm.

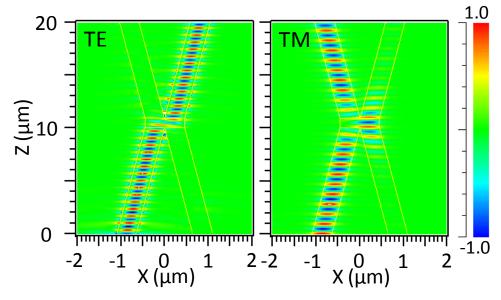

Assuming  $W_{TMI}$ =900nm, h=230nm and wavelength,  $\lambda$ =1550nm, we simulate the device in Fig. 1(a) using the full vectorial eigenmode decomposition-based complex Film Mode Matching (FMM) solver (with 60 1D modes) of the FIMMPROP module. Fig. 1(b) shows the variations of power splitting ratio, P4/P3 and P3/P4, versus  $L_{TMI}$  for input TE and TM polarizations, respectively. One notes that  $\varphi$  depends on both polarization and the angle between the access waveguides,  $\theta$ . Also, for a TM polarized input, a change in  $\theta$  has a considerably large effect on  $\varphi$ . This is not surprising, as the TM mode supported by the access waveguides is much less confined compared to the TE mode. Thus, for a TM input, the coupling between the two access waveguides is considerably stronger resulting in an effectively larger  $L_{TMI}$  that is more sensitive to  $\theta$  than that for a TE input. Since the power splitting ratio changes much slowly with  $\theta$  for a TE polarized input, the easily tunable  $\theta$  can be used as a reliable design parameter for tuning the output SR.

Figure 1(b) shows that at  $\theta$ =7.4° and  $L_{TMI}$ =0.94µm, the 2x2 PS device operates in the cross and bar states for TE and TM polarized inputs, respectively. Note that  $L_{TMI}$ =0.94µm is shorter than both  $L_{\pi}^{TE} = 1.80 \mu m$  and  $L_{\pi}^{TM} = 2.31 \mu m$ . Fig. 2 shows the field propagation through this device from FDTD (RSoft<sup>TM</sup>) simulations,

which indicate that at  $\theta=7.4^{\circ}$ ,  $L_{TMI}=0.94\mu$ m effectively corresponds to  $2L_{\pi}^{TM}$  and  $1L_{\pi}^{TE}$ . SR values for TE and TM inputs are P4/P3=19.4dB and P3/P4=18.6dB, respectively. Insertion loss values for TE and TM inputs are P3/P1=-0.25dB and P4/P1=-0.35dB, respectively.

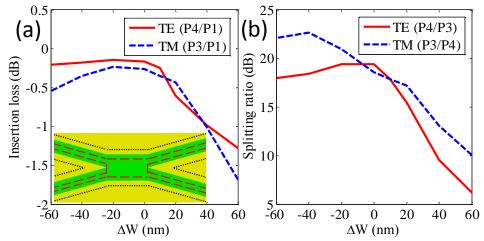

Based on our simulation results the device performance becomes independent of the input/output access waveguide length when they are longer than 6.5 $\mu$ m. Thus, the total device length, including the input/output access waveguides, is 13.94 $\mu$ m. Ultracompact directional coupler based PSs with similar dimensions have been reported [9][10]. As discussed before, the fabrication tolerance remains an issue for short directional couplers with small gap sizes. In order to investigate the proposed PS fabrication tolerance, we assume that the fabrication errors appear as changes in waveguide width ( $\Delta$ W) [2].

Fig. 2-3. Variations of (a) insertion loss and (b) polarization splitting ratios functions of deviation in the waveguide width for input TE and TM polarizations. The inset of (a) shows a PS layout affected by  $\Delta W < 0$  (dashed red) and  $\Delta W > 0$  (dotted black).

The device layout changes due to  $\Delta W < 0$  and  $\Delta W > 0$  are depicted in Fig. 3(a) inset. A  $\Delta W < 0$  does not change the TMI length while widening the gap between the access waveguides. When the waveguide width increases ( $\Delta W > 0$ ), one can imagine that the *effective* TMI length increases but the *effective* gap between the access waveguides is just shifted away from the original TMI.

Variations of insertion loss and SR with  $\Delta W$  for TE and TM polarized inputs are shown in Figs. 3(a) and (b), respectively. TM mode propagation in the access waveguides is near the mode cut-off, and a reduction in the waveguide width ( $\Delta W < 0$ ) results in a significantly less confined modal field. Thus, in the case of TM input, the effect of wider gap due to  $\Delta W < 0$  is compensated by the stronger coupling between the more spread-out modal fields. As the coupling at the access waveguides does not play a significant role for TE polarization, the PS device is tolerant to  $\Delta W < 0$  for both TE and TM polarizations.

On the other hand, a  $\Delta W > 0$  effectively increases the TMI length as  $\Delta L = \Delta W/\sin(\theta/2) = 15.5 \Delta W$ . In other words,  $\Delta L/L \approx 15 \Delta W/W$ . Note that for the self imaging process in the TMI to be tolerant to small changes in the TMI width, the changes in the (effective) TMI length must satisfy  $\Delta L/L = 2\Delta W/W$  [7]. Therefore, the large changes in the MMI length rapidly degrade the TMI performance for  $\Delta W > 10$ nm, for both TE and TM polarized inputs in a similar way. Note that for  $\Delta W < 0$ , the device fabrication tolerance is comparable to that of a tapered asymmetric directional coupler, which is nearly 500 times larger [2].

To benefit from tolerance to  $\Delta W < 0$ , we choose a fabrication process with a possible shrinkage in the waveguide width. For  $\Delta W < 0$ , the minimum distance between the access waveguides on each side is given as  $\Delta W \cos(\theta)$ . For  $\Delta W < 0$ , the tip shape between the access waveguides is blunt and does not introduce fabrication difficulties. The PS device is fabricated on Soitec SOI wafers consisting of 3 micron thick silicon dioxide and 250 nm thick top silicon device layer. The top silicon layer is oxidized to create a 45 nm top silicon dioxide layer, which serves as a hard mask in the silicon etch process.

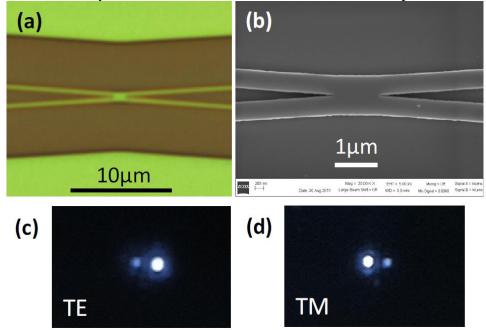

Fig. 2-4. Microscope (a) and SEM(b) images of the fabricated PS device. Top-down IR pictures of the PS outputs for TE (c) and TM (d) polarized inputs.

The oxidation process consumes 20nm of the top silicon layer and results in a final 230nm silicon layer. The top oxide layer is patterned using electron beam lithography and CHF3/O2 plasma based reactive ion etching (RIE). The pattern is then transferred to the silicon layer underneath by HBr/Cl2 based RIE. In addition to a small etch undercut, due to the E-beam proximity effect, the area of the exposed positive resist (ZEP520) expands a little bit resulting in narrowing of the unetched areas of the top silicon layer. Overall, with this fabrication process,  $\Delta W < 0$  is expected. Microscope and SEM images of the fabricated PS are shown in Fig. 4. Top-down SEM measurements indicate a final  $\Delta W$ =-20nm.

The PSs are tested on a Newport six-axis auto-aligning station. A broadband amplified spontaneous emission (ASE) source output light, covering 1520~1620 nm, is TE- or TM-polarized with an extinction ratio of over 30dB and butt coupled into/out of the input/output waveguide facets through a polarization maintaining lensed fiber. Top-down IR pictures of the outputs at the chip edge with TE and TM polarized input excitations are shown in Fig. 4.

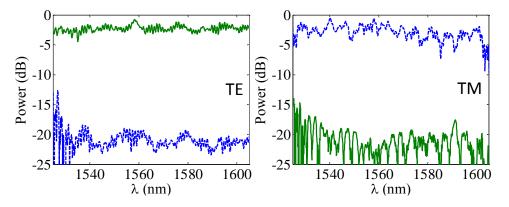

Fig. 5 shows the spectra of normalized output power measured at Port 3 and Port 4, for TE and TM input excitations at Port 1. The results indicate polarization splitting ratios of P4/P3=18.2dB and P3/P4=16.8dB, respectively, for the TE and TM polarized inputs at  $\lambda$ =1550nm. The splitting ratio

remains better than 15dB over a 70nm bandwidth for the TE polarized input and over 50nm bandwidth for the TM polarized input. The TE and TM propagation losses in a fabricated 450nm x 230nm waveguide are estimated to be 7.5dB/cm and 16.3dB/cm, respectively, using a cutback technique, at  $\lambda$ =1550. In order to accurately estimate the device insertion loss, while excluding the input/output fiber/waveguide coupling loss and propagation losses in the access waveguides, we compare the transmission through two-stage cascaded TMIs with the transmission through a single TMI for each polarization. A narrowband laser ( $\lambda$ =1550) is used for insertion loss measurements. Our results indicate that the insertion loss is 0.8dB for the TE polarized input and 1.7dB for the TM polarized input.

Fig. 2-5. Normalized output transmission spectra at P3 (dashed blue) and P4 (solid green) for TE and TM input excitations at P1. Data is normalized to the measured ASE output spectrum.

In summary, we presented the design and fabrication of a TMI based PS, for which the length of the TMI section is reduced to less than a single beat-length of the TE mode. While the device performance is sensitive to the angle between the two input/output access waveguides, the device is rather tolerant to width variations (shrinkage) in the TMI and the access waveguides. To the best of our knowledge, this TMI is the most compact and largest bandwidth self-imaging device demonstrated so far.

This research is supported by the multi-disciplinary university research initiative (MURI) program through the AFOSR, contract # FA 9550-08-1-0394.

### References

- [2-1] S. Corzine, P. Evans, M. Fisher, J. Gheorma, M. Kato, V. Dominic, P. Samra, A. Nilsson, J. Rahn, I. Lyubomirsky, A. Dentai, P. Studenkov, M. Missey, D. Lambert, A. Spannagel, S.Murthy, E. Strzelecka, J. Pleumeekers, A. Chen, R. Schneider, R.Nagarajan, M. Ziari, J. Stewart, C. Joyner, F. Kish, and D. Welch, IEEE Photon. Tech. Lett. 22(14), 1015–1017 (2010).

- [2-2] Luc M. Augustin, Jos J. G. M. van der Tol, RabahHanfoug, Wim J. M. de Laat, Michael J. E. van de Moosdijk, Paul W. L. van Dijk, Yok-Siang Oei, and Meint K. Smit, J. Lightwave Technol. 25, 740-746 (2007).

- [2-3] I. Kiyat, A. Aydinli, and N. Dagli, IEEE Photon. Technol. Lett. 17, 100-102 (2005).

- [2-4] J. M. Hong, H. H. Ryu, S. R. Park, J. W. Jeong, S. G. Lee, E.-H. Lee, S.-G. Park, D. W. Woo, S. Kim, and B.-H. O, IEEE Photonics Technol. Lett. 15, 72–74 (2003).

- [2-5] B.-K. Yang, S.-Y. Shin, and D. Zhang, IEEE Photon. Technol. Lett. 21(7), 432–434 (2009).

- [2-6] D. M. Mackie, T. J. Tayag, and T. E. Batchman, Opt. Eng. 40, 2265–2272 (2001).

- [2-7] P. A. Besse, M. Bachmann, H. Melchior, L. B. Soldano, and M. K. Smit, J. Lightwave Technol. 12, 1004–1009 (1994).

- [2-8] F. Rottmann, A. Neyer, W. Mevenkamp, and E. Voges, J. Lightwave Technol. 6, 946-952 (1988).

- [2-9] Hiroshi Fukuda, Koji Yamada, Tai Tsuchizawa, Toshifumi Watanabe, Hiroyuki Shinojima, and Sei-ichi Itabashi, Opt. Express 14, 12401-12408 (2006).

- [2-10] S. Lin, J. Hu, and K. Crozier, Appl. Phys. Lett. 98, 151101 (2011).

# **3.0** Ultralow-loss polycrystalline silicon waveguides and high uniformity 1x12 MMI fanout for 3D photonic integration

## 1. Introduction

On-chip photonic networks are a promising solution for the interconnect bottleneck in high performance microelectronics. Crystalline silicon-on-insulator (SOI) is the most commonly used photonics platform due to its large index contrast with silicon dioxide ( $\Delta n \sim 2.02$ ), which enables submicron waveguides and small bending radii. In addition, SOI exhibits excellent material properties such as low bulk absorption at telecom wavelengths and high electronic carrier mobility. While crystalline SOI is the most desirable, photonic devices would be restricted to the electronic layer. Furthermore, silicon photonics requires a thick Buried Oxide (BOX) layer (typically a few micrometers) for optical isolation from the substrate, but SOI for electronics requires a thin oxide layer ranging from tens to hundreds of nanometers to allow thermal flow into the substrate [Sherwood-Droz2011]. Although it has been shown that SOI for electronics can also be used for photonics [Holzwarth2008], it comes generally at the cost of more real estate and adds greater complexity and cost to the standard CMOS fabrication process. A multi-layer platform would enable photonic device versatility, as footprint and separation issues are mitigated.

In order to maximize such a platform's design flexibility, CMOS compatible silicon deposition methods are strongly desired. As it is not currently possible to deposit crystalline silicon, alternative materials must be considered. Silicon nitride is a low loss material that has been used for multilayer photonic integration [Sherwood-Droz2011], but its lower index contrast increases device footprint, and it also lacks any mechanism for high-speed modulation, limiting nitride solely to passive devices. Hydrogenated amorphous silicon deposited by Plasma-Enhanced Chemical Vapor Deposition (PECVD) is a low loss material that has been used in multilayer stacks[Kang2011], but sufficient and stable hydrogenation of the silicon dangling bonds are critical to maintaining its low loss property. Zhu et al have demonstrated that the propagation loss for hydrogenated amorphous silicon waveguides starts to increase rapidly at temperatures above 300°C [Zhu2010], and Selvaraja et al have shown that the refractive index change measured from a Mach-Zehnder Interferometer (MZI) starts to occur at 200°C[Selvaraja2010]. In addition to thermal stability of hydrogenated amorphous silicon, another significant challenge is that the charge mobility is very low due to the amorphous structure of the film, thereby limiting its application in high-speed applications.

Deposition of polycrystalline silicon (polysilicon) is a mature, CMOS compatible process that is easy to deposit on a variety of substrates. In addition, it can be easily doped to realize electrically active photonic devices due to its relatively high (~100cm<sup>2</sup>/V-s) [1] electronic carrier mobility. Propagation loss has remained a significant challenge for polysilicon waveguides, which is dominated by scattering and absorption at the polycrystalline grain boundaries. Low loss (~6.45dB/cm) polysilicon waveguides, [2, 3] high quality factor ring resonators [4], and high speed electro-optic modulators [5] formed by Solid Phase Crystallization (SPC) of Low Pressure Chemical Vapor Deposition (LPCVD) amorphous silicon have been demonstrated. Compared to direct deposition of LPCVD polysilicon, SPC of LPCVD amorphous silicon yields superior film qualities, such as smoother surfaces to reduce interfacial scattering and larger grains that result in fewer absorbing and scattering boundaries, further lowering the propagation loss [6].

To date, photonic polysilicon research has focused on waveguides and devices in the single mode region with thicknesses of 200-250nm and widths of 300-500nm, where narrower waveguides result in lower loss due to less confinement of light in the polysilicon core, indicating that attenuation is dominated by bulk loss [2]. Indeed, efforts to further reduce the overlap of the optical mode with the waveguide cross section have been made by forming polysilicon waveguides in the same step as the polysilicon transistor gate for electronics, resulting in core geometries of 120nm X 350nm and a propagation loss of 6.2 dB/cm at 1550nm. Unfortunately, little work exists for wider, multimode polysilicon devices. Liao et al have reported that thicker and wider polysilicon waveguides suffer from higher propagation losses due to increased optical confinement[Liao2000]. However, for key photonic components such as multimode interference couplers (MMI) for beam splitting and arrayed waveguide gratings (AWG) for wavelength division multiplexing (WDM), device dimensions can span tens to hundreds of microns in width [7, 8]. Characterizing the loss of polysilicon at such widths is necessary to determine if these devices can be formed without prohibitively high losses.

In this paper, we fabricate polysilicon waveguides of various widths and investigate the propagation loss dependence of these waveguides on the waveguide width and also compare with the same structures on crystalline SOI. We find that as the waveguide width increases, the propagation loss for both polysilicon and crystalline silicon waveguides decreases. At the widest waveguide width of 10 $\mu$ m, both polysilicon and crystalline silicon have low loss values of 0.56dB/cm and 0.31dB/cm, respectively, indicating very little bulk absorption occurs in the polysilicon film. To the best of our knowledge, this is the lowest demonstrated loss for polysilicon waveguides to date. Moreover, the first 1x12 polysilicon MMI is presented with an insertion loss of -1.29dB and a uniformity of 1.07dB.

### 2. Design and Fabrication

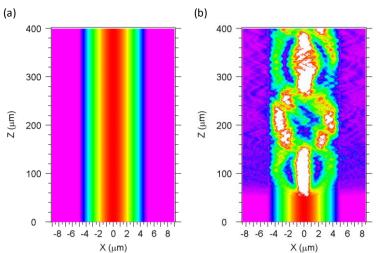

We have used the beam propagation method (BPM) from Rsoft to simulate  $10\mu m$  wide waveguides for both crystalline silicon and polysilicon with grain boundaries, which is shown in Figure 2 (a) and (b), respectively. Figure 2(a) shows the  $10\mu m$  wide crystalline silicon waveguide excited by the fundamental mode, which propagates through the waveguide undisturbed. In contrast, a polysilicon waveguide is simulated by adding grain boundaries. The grain boundaries scatter light into higher order modes that are still guided by the wide waveguide. For narrower waveguides, the grain boundaries scatter light into radiative modes, as higher order modes are not guided. Therefore, the number of guided modes in a given waveguide geometry determines the propagation loss due to grain boundary scattering.

Figure 3-1-Beam Propagation Method simulation of 10µm waveguide for (a) crystalline silicon and (b) polysilicon with grain boundaries.

In order to investigate the effect of the waveguide width on the propagation loss of polysilicon waveguides, the waveguide width is varied by using the structure shown in Figure 2. For each waveguide width, the input and output waveguides have the same dimensions to equalize the coupling conditions. We first adiabatically taper all waveguide widths to 500 nm in order to filter out higher order modes and achieve single mode propagation. The waveguide is then adiabatically tapered to the desired waveguide width, which ranges from 400 nm to 10  $\mu$ m. After 5 nm of propagation, all waveguides are then tapered back to the output waveguide width. The same structures are also fabricated on crystalline silicon as a reference. By having the exact same structure and fabrication process, our results can only arise from the differences between the two materials.

Figure 3-2-Schematic of multimode waveguide structure. Not drawn to scale.

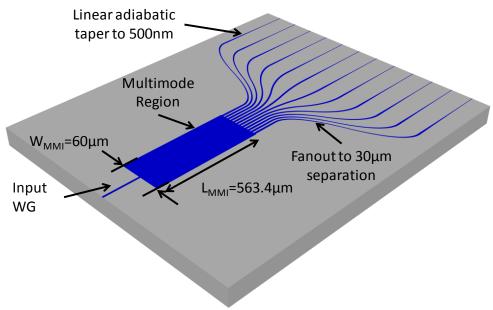

In addition, we also designed a 1x12 Multimode Interference (MMI) optical beam splitter to further demonstrate large multimode polysilicon devices. The length and width of the multimode region are  $L_{MMI}$ =563.4 µm and  $W_{MMI}$ =60 µm respectively. The input and access waveguides are both 2.6 µm wide. To clearly resolve the individual output spots in the near field, a fanout design was used to separate the 12 MMI output channels to 30 µm. A schematic of the 1x12 MMI can be seen in Figure 3.

Figure 3-3-Schematic of 1x12 MMI

In our experiment, we thermally oxidize a bare silicon wafer to create  $2.0\mu m$  of SiO<sub>2</sub> which acts as the BOX layer and is thick enough to prevent optical leakage into the substrate. Afterwards, a 250nm thick layer of amorphous silicon was deposited using Low Pressure Chemical Vapor Deposition (LPCVD) at 550°C. From [Hatalis1998], we find that the deposition rate should be sufficiently high to minimize the number of nucleation sites, which results in increased grain size. Consequently, we use an increased silane gas flow to achieve a deposition rate of 3.3nm/minute. After the amorphous silicon deposition, we briefly dip the wafers in Piranha solution to form a native oxide layer. This thin native oxide layer stabilizes the top surface of the amorphous silicon and prevents increased surface roughness during future anneal treatments[Ibok93]. The wafers are then annealed using a two-step annealing process. The first anneal is a low temperature anneal that is done at  $600^{\circ}$ C N<sub>2</sub> for 40 hours, and the purpose of this anneal is for gradual grain nucleation, which results in large grains. The second anneal is a 5 hour 1000°C also in N<sub>2</sub>, and this step is to crystallize the individual polysilicon grains.

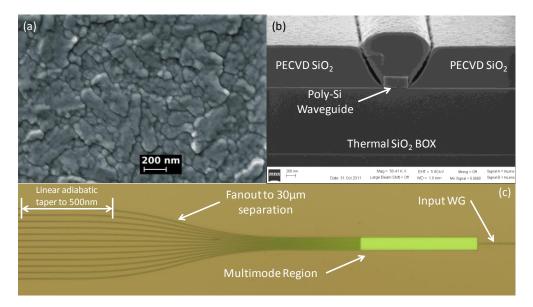

In order to estimate our grain size, we use dry oxidation at 900°C for 30 minutes to oxidize the top surface of our polysilicon film. Because polysilicon grains will preferentially oxidize along grain boundaries, we can use Buffered Oxide Etch (BOE) to remove the oxide and then use

Scanning Electron Microscopy (SEM) to visualize our grains. A picture of such an SEM image is shown in Figure 5(a), and we estimate the grain sizes to be ~300nm.

A 45nm layer of PECVD SiO<sub>2</sub> is deposited to serve as an etching hard mask. Our waveguides were patterned using a JEOL 6000FS electron-beam lithography system with ZEP520 resist, and etched with HBr/Cl<sub>2</sub> based Reactive Ion Etching (RIE). Afterwards, a 1 $\mu$ m thick film of SiO<sub>2</sub> for top cladding was deposited using PECVD. A cross section view of a single mode polysilicon waveguide is shown in Figure 5(b), and a microscope image of the 1x12 MMI is shown in Figure 5(c).

Figure 3-4-(a) Top down SEM image of polysilicon grains after oxidation and BOE, (b) cross sectional SEM of a single mode polysilicon waveguide and (c) microscope image of the completed 1x12 MMI.

## 3. Results and Analysis

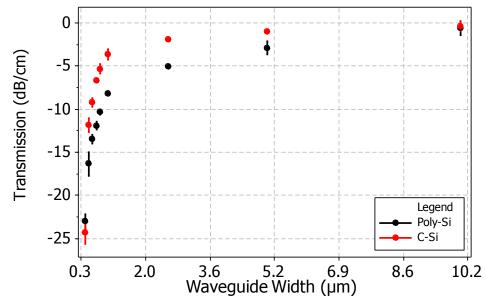

Transverse Electric (TE) polarized light at 1550nm was coupled into and out of the waveguides using lensed fibers with 2.5  $\mu$ m mode field diameters, where the input is a polarization maintaining (PM) fiber, and the output is collected with a single mode (SM) fiber. The propagation loss of various waveguide widths for both crystalline and polysilicon are shown below in Figure 5.

Figure 3-5-Propagation loss of various polysilicon and crystalline silicon waveguide widths. Standard error bars are given for each data measurement.

The propagation loss decreases for both crystalline silicon and polysilicon as the waveguide width increases. At a waveguide width of 400nm, the propagation losses of crystalline and polysilicon are virtually the same, but as the waveguide width increases, the loss difference between the two also increases. For waveguide widths above 2.5µm, the difference in propagation loss between crystalline and polysilicon decreases until they have nearly identical propagation losses at 10µm. For crystalline silicon, this behavior is well known and is due to decreasing sidewall interaction of the fundamental mode of the waveguide. However, the grain boundaries present in polysilicon cause scattering to either radiation modes or higher order modes depending on whether the waveguide width supports the higher modes. This scattering causes the additional loss between polysilicon and crystalline waveguides of the same width. It is important to note that at a 10µm waveguide width, both polysilicon and crystalline silicon waveguides have the lowest losses of 0.56dB/cm and 0.31dB/cm, respectively. To our knowledge, this value is the lowest propagation loss for a polysilicon waveguide to date. Furthermore, it indicates that there is very little bulk absorption from the polysilicon grain boundaries. This behavior of decreasing propagation loss with increasing waveguide width validates the use of large polysilicon waveguides in photonic integrated circuits.

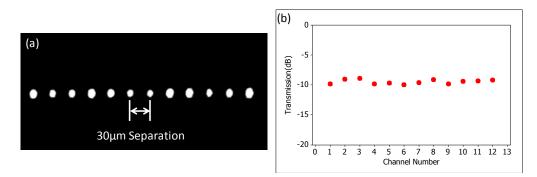

We also tested our 1x12 MMI to demonstrate a large polysilicon device. As before, TE polarized light at 1550nm was coupled into the 1x12 MMI. Using an IR camera, 12 output spots are imaged from the MMI fanout, which are shown in Figure 6(a). To characterize the performance of this 1x12 MMI, we used lensed fiber to collect each of the 12 output intensities. The performance of an MMI can be described by output uniformity and insertion loss. The uniformity is calculated as  $10\log(I_{max}/I_{min})$ , where  $I_{max}$  and  $I_{min}$  are the maximum and minimum

output intensities of the MMI, respectively. The insertion loss of the MMI is defined as  $-10\log(\sum I_i/I_{in})$ , where  $I_i$  is the output intensity of the *i*<sup>th</sup> output channel, and  $I_{in}$  is the intensity of a straight waveguide with the same dimensions of the MMI input waveguide. For our polysilicon 1x12 MMI, we determine a uniformity of 1.07dB and an insertion loss of -1.29dB. The insertion loss is a negative number because the output intensity of the input waveguide used for normalization is lower than the sum of the MMI output intensities. This is due to the presence of the multimode region of the MMI, which is 60µm wide and 563.4µm long and has a much lower loss compared to the much narrower input waveguide. We have previously demonstrated a 1x12 MMI on crystalline silicon with comparable performance [10].

Figure 3-6-(a) IR image of the 12 output spots from 1x12 MMI fanout. (b) Output intensities of the 1x12 polysilicon MMI.

### 4. Conclusion

We have investigated the feasibility of multimode polysilicon waveguides to demonstrate the suitability of polysilicon as a candidate for multilayer photonic applications. SPC with a maximum temperature of 1000°C is used to create polysilicon on thermal SiO<sub>2</sub>. We then measure the propagation losses for various waveguide widths on both polysilicon and crystalline silicon platforms. We find that as the width increases for polysilicon waveguides, the propagation loss decreases similarly to crystalline silicon waveguides. The difference in loss between the two platforms for a given waveguide width is due to the scattering from the polysilicon grain boundaries, which excites higher order modes. Depending on the waveguide width, these modes either propagate as higher order modes or are lost as radiation modes. We also find that at a waveguide width of 10µm, the polysilicon propagation loss of 0.56dB/cm is very close to the crystalline silicon propagation loss of 0.31dB/cm, indicating that there is little bulk absorption from the polysilicon. This result validates the use of polysilicon waveguides in photonic integrated circuits. We further demonstrate this with a 1x12 polysilicon MMI that has a low insertion loss of -1.29dB and a high uniformity of 1.07dB. Together, we present the lowest propagation loss for polysilicon waveguides to date of 0.56dB/cm as well as the first 1x12 polysilicon MMI.

#### Acknowledgements

This research is supported by the Multi-disciplinary University Research Initiative (MURI) program through the AFOSR, Contract No. # FA 9550-08-1-0394.

#### References

- [3-1] T. Kamins, Polycrystalline Silicon for Integrated Circuits and Displays, 2nd ed. (Kluwer, 1998).

- [3-2] Shiyang Zhu, Q. Fang, M. B. Yu, G. Q. Lo, and D. L. Kwong, "Propagation losses in undoped and n-doped polycrystalline silicon wire waveguides," Opt. Express 17, 20891-20899 (2009).

- [3-3] Q. Fang, J. F. Song, S. H. Tao, M. B. Yu, G. Q. Lo, and D. L. Kwong, "Low loss (~6.45dB/cm) sub-micron polycrystalline silicon waveguide integrated with efficient SiON waveguide coupler," Opt. Express 16, 6425-6432 (2008).

- [3-4] Kyle Preston, Bradley Schmidt, and Michal Lipson, "Polysilicon photonic resonators for large-scale 3D integration of optical networks," Opt. Express 15, 17283-17290 (2007).

- [3-5] Kyle Preston, SasikanthManipatruni, Alexander Gondarenko, Carl B. Poitras, and Michal Lipson, "Deposited silicon high-speed integrated electro-optic modulator," Opt. Express 17, 5118-5124 (2009).

- [3-6] L. Liao, D. R. Lim, A. M. Agarwal, X. Duan, K. K. Lee, and L. C. Kimerling, "Optical transmission losses in polycrystalline silicon strip waveguides: effects of waveguide dimensions, thermal treatment, hydrogen passivation, and wavelength," J. Electron. Mater. 29(12), 1380–1386 (2000).

- [3-7] A. Hosseini et al, "1xN multimode interference beam splitter design techniques for onchip optical interconnections," IEEE Journal of Selected Topics in Quantum Electronics 17, 510-515 (2011).

- [3-8] P. Dumon, W. Bogaerts, D. Van Thourhout, D. Taillaert, R. Baets, J. Wouters, S. Beckx, and P. Jaenen, "Compact wavelength router based on a Silicon-on-insulator arrayed waveguide grating pigtailed to a fiber array," Opt. Express 14, 664-669 (2006).

- [3-9] Liao, L., Lim, D. R., Agarwal, A. M., Duan, X., Lee, K. K., &Kimerling, L. C., "Optical transmission losses in polycrystalline silicon strip waveguides: Effects of waveguide dimensions, thermal treatment, hydrogen passivation, and wavelength," Journal of Electronic Materials, 29(12), 1380-1386 (2000).

- [3-10] EffiongIbok and ShyamGarg, "A Characterization of the Effect of Deposition Temperature on Polysilicon Properties," J. Electrochem. Soc. 140, 2927 (1993).

- [3-11] Kwong, D.; Zhang, Y.; Hosseini, A.; Liu, Y.; Chen, R.T.; , "1 X 12 even fanout using multimode interference optical beam splitter on silicon nanomembrane," Electronics Letters , vol.46, no.18, pp.1281-1283, September 2010

- [3-12] Jason S. Orcutt, Sanh D. Tang, Steve Kramer, Karan Mehta, Hanqing Li, Vladimir Stojanović, and Rajeev J. Ram, "Low-loss polysilicon waveguides fabricated in an emulated high-volume electronics process," Opt. Express 20, 7243-7254 (2012)

- [3-13] Kyle Preston and Michal Lipson, "Slot waveguides with polycrystalline silicon for electrical injection," Opt. Express 17, 1527-1534 (2009)

- [3-14] Nicolás Sherwood-Droz, Alexander Gondarenko, and Michal Lipson, "Oxidized Silicon-On-Insulator (OxSOI) from bulk silicon: a new photonic platform," Opt. Express 18, 5785-5790 (2010)

- [3-15] C. W. Holzwarth, J. S. Orcutt, H. Li, M. A. Popovic, V. Stojanovic, J. L. Hoyt, R. J. Ram, and H. I. Smith, "Localized Substrate Removal Technique Enabling Strong-Confinement Microphotonics in Bulk Si CMOS Processes," in Conference on Lasers and Electro-Optics/Quantum Electronics and Laser Science Conference and Photonic

Applications Systems Technologies, OSA Technical Digest (CD) (Optical Society of America, 2008), paper CThKK5.

- [3-16] Nicolás Sherwood-Droz and Michal Lipson, "Scalable 3D dense integration of photonics on bulk silicon," Opt. Express 19, 17758-17765 (2011)

- [3-17] Shiyang Zhu, G. Q. Lo, and D. L. Kwong, "Low-loss amorphous silicon wire waveguide for integrated photonics: effect of fabrication process and the thermal stability," Opt. Express 18, 25283-25291 (2010)

- [3-18] JoonHyun Kang, Yuki Atsumi, Manabu Oda, Tomohiro Amemiya, Nobuhiko Nishiyama and Shigehisa Arai, "Low-Loss Amorphous Silicon Multilayer Waveguides Vertically Stacked on Silicon-on-Insulator Substrate," Jpn. J. Appl. Phys. 50 (2011) 120208.

- [3-19] Shankar Kumar Selvaraja, WimBogaerts, Dries VanThourhout, and Marc Schaekers, "Thermal trimming and tuning of hydrogenated amorphous silicon nanophotonic devices," Appl. Phys. Lett. 97, 071120 (2010).

- [3-20] Hatalis, Miltiadis K.; Greve, David W.; , "Large grain polycrystalline silicon by low-temperature annealing of low-pressure chemical vapor deposited amorphous silicon films," Journal of Applied Physics , vol.63, no.7, pp.2260-2266, Apr 1988

## 4.0 Vertically Integrated Double-layer On-chip Silicon Membranes for 1-to-12 Waveguide Fanouts

Large on- and off-chip bandwidths required for high performance multi-core structures (~10TB/s by 2015) corresponding to interconnect energy budgets of ~100 fJ/bit will render optical components essential parts of future high performance integrated systems [1-3]. Complementary metal-oxide-semiconductor (CMOS) compatible silicon photonics, which allows for integration of optical components on the same silicon chip with CMOS transistors, is consideredone of the solutions to such a high demand for low energy and high bandwidth communications [3, 4]. Since the Luxtera silicon photonic chip in 2002, the number of on-chip photonic components has doubled each year [5, 6]. There is also a "Moore's law like" trend observed inInP-based photonic integrated circuit (PIC) development since 1988 [7]. However, due to the large sizes of the on-chip photonic components, single layer photonic component counts cannot exceed1000 and 10,000 in InP and silicon PICs, respectively [8].

Vertical integration of multiple layers of active and passive components can resolve the problem of limited real estate on a single layer [9]. So far, an extra polysilicon layer on top of the crystalline silicon layer has been used for CMOS microelectronics and photonics integration [10, 11]. This scheme may also be used for three-dimensional (3D) photonics integration. However, the optical losses in polysilicon waveguides are dominated by scattering and absorption at the grain boundaries [10], which increase significantly when the waveguide width shrinks to below 200nm [12]. Techniques such as high temperature annealing, special hydrogen plasma passivation steps, and patterning waveguides before the solid-phase crystallization (SPC) of deposited amorphous silicon were shown to reduce the propagation loss [12, 13]. Lowest losses ranging from 7dB/cm to 13dB/cm were reported in polycrystalline silicon waveguides with cross sectional dimensions of approximately 450 x 250 nm [12, 14, 15], and from 1dB/cm to 2dB/cm in crystalline silicon waveguides withsimilar dimensions [16, 17]. Additionally, if the temperature process is limited to about 600°C, which is compatible with standard CMOS processes, the Q-factor of the ring resonators fabricated on polysilicon layers drops by an order of magnitude [10, 18], indicating even higher losses.

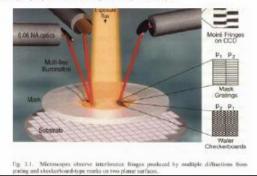

In this paper we demonstrate a 3D photonic integration of self-alignedstructures using double-bonded silicon-on-insulator (SOI) wafers by fabricating double-layer 1x12 multimode interference (MMI) couplers on silicon membranes. Using the presented scheme, multi-levels of PICs including waveguide arrays, MxN MMI couplers, and arrayed waveguide gratings (AWGs) can be vertically integrated to significantly increase the on-chip integrated photonic component count.

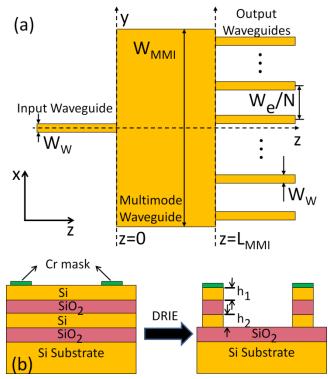

The schematic of a 1xN MMI coupler is shown in Figure 1(a). We choose the MMI width,  $W_{MMI}$ =60µm. The MMI length with a 1xN fanout is given as  $L_{MMI} = (n_{eff} W_{MMI}^2)/(\lambda_0 N) = 664$ µm [19], where  $n_{eff}$ =3.43 (for 1.3µm thick silicon membrane) is the effective refractive index of the transverse electric (TE) fundamental mode of the multimode waveguide, and  $\lambda_0 = 1.55$ µm is the free space wavelength. The input and output access waveguide widths,  $W_w = 2.5$ µm, match the mode sizes of the input/output lensed fibers. Thus, the fiber-waveguide coupling tolerance is enhanced due to the waveguides' relatively large end-fire cross sections. The schematic of the double-bonded SOI wafer and self-aligned waveguide structure are shown in Figure 1(b). The thicknesses of both silicon layers are  $h_1=h_2=1.3$ µm, and the two buried oxide (BOX) layers are both 2.0µm thick. The simulated effective index of the fundamental TE and transverse magnetic (TM) modes in the access waveguides are 3.417 and 3.412, respectively, at  $\lambda$ =1.55µm. Polarization independent operation is expected due to the small difference between the TE and TM effective indices. We fabricate two self-aligned 1x12 MMI couplers on two vertically stacked silicon membrane layers using one lithography process followed by a single etching step. MMI couplers can be used for efficient on-chip beam splitting [19]. A complete analysis for a symmetrically excited 1xN MMI coupler with uniform output was presented in Ref. [20].

FIG.4-1.(a) The Schematic of a 1xN MMI coupler. (b) The schematic of the double-bonded SOI wafer and self-aligned waveguide structure.

The double-bounded SOI wafers are fabricated using fusion bonding and etch-back [21], and are commercially available from Ultrasil. A 100nm thick chromium etching mask is defined through an ebeam lithography and lift-off process. The pattern is then transferred to both silicon layers using one SF<sub>6</sub>/C<sub>4</sub>F<sub>8</sub>/Ar based Deep Reactive-Ion-Etching (DRIE) step in Plasma-Therm'sVersaline system. The DRIE process consists of ~1000 iterations of a two-step polymer deposition/etching cycle. Afterwards, the chromium mask is removed. The sidewall profile control in the DRIE process is the key to the performance of the fabricated devices. Although the Bosch process based DRIE of silicon, which alternates repeatedly betweendeposition of a polymer passive layer and isotropic plasma etching of silicon, is well developed in industry [22] and the standard recipes are provided by the system manufacturer, it has a very slow etch rate for silicon oxide and is not applicable for etching into double-bonded SOI wafers. In order to achieve a vertical sidewall,several process parameters need to be optimized, including gas composition, bias radio frequency (RF) voltage, inductively coupled plasma (ICP) power, chamber pressure, and step time. A standard recipe (Table I) for etching SOI wafers is used as the base recipe for parameter optimization. Wafer loading and temperature are kept constant during the optimization process.

| Steps          | Gas flow rate (sccm <sup>a</sup> )SF6C4F8 |           |          | Ar        | Bias RF<br>voltage<br>(V) |           | ICP<br>power<br>(W) |           | Pressure<br>(mTorr) |           | Time (s) |           |          |           |

|----------------|-------------------------------------------|-----------|----------|-----------|---------------------------|-----------|---------------------|-----------|---------------------|-----------|----------|-----------|----------|-----------|

|                | Bas<br>e                                  | Fin<br>al | Bas<br>e | Fin<br>al | Bas<br>e                  | Fin<br>al | Bas<br>e            | Fin<br>al | Bas<br>e            | Fin<br>al | Bas<br>e | Fin<br>al | Bas<br>e | Fin<br>al |

| Depositi<br>on | 50                                        | 50        | 125      | 125       | 10                        | 10        | 10                  | 10        | 160<br>0            | 160<br>0  | 20       | 20        | 0.8      | 0.8       |

| Etching        | 60                                        | 50        | 40       | 40        | 10                        | 10        | 250                 | 400       | 120<br>0            | 150<br>0  | 20       | 20        | 2        | 2         |

TABLE 4-I.DRIE base and final parameters for one deposition and etching cycle.

<sup>a</sup>SCCM denoted standard cubic centimeter per minute at standard temperature and pressure (STP).

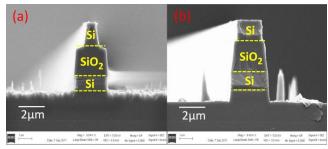

By individually optimizing these parameters to achieve vertical sidewalls, we arrive at the final recipe, which is also shown in Table I. We determine that the bias RF voltage has the largest impact on the anisotropy of the sidewall profile. A larger bias RF voltage results in a higher etch rate and yields a more vertical sidewall profile during silicon oxide etching, but it also causes more damage to the polymer layer on the sidewall of the silicon membrane layer. Figure 2(a) shows the cross section of a waveguide etched usingour otherwise final recipe with a 450V bias RF voltage. The polymer layer on the sidewall is consumed the etching step and results in a large undercut to the top silicon layer, leading to significant deviation from the original design. Figure 2(b) shows the cross section of a waveguide etched using the silicon of a reduced undercut and a ~80°tapered sidewall profile during the silicon oxide etching. The undercut to the top silicon layer is inevitable due to the required ~40 minute etch time of the BOX layer [23].

FIG.4-2. SEM images of the waveguide cross section under different etching conditions, (a) a waveguide cross section with large undercut, (b) a waveguide cross section with corrected undercut.

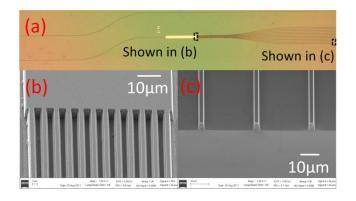

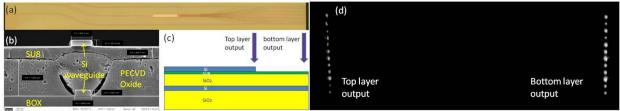

The fabricated MMI access waveguides are 2.0µm and 2.9µm wide on the top and bottom layers, respectively. These access guides also correspond to TE fundamental mode effective refractive indices of 3.410 and 3.419, respectively [Figure 2(b)]. We note that because of the large thicknesses of the silicon layers, the effective index changes negligibly with variations in the waveguide width. Figure 3(a) shows a microscope image of the overall double-layer MMI. Figures 3(b) and 3(c) show the scanning electron microscope (SEM) images of the MMI output region and the output facet, respectively, with their corresponding locations labeled in Figure 3(a).

FIG.4-3.(a) Optical microscope image of the double-layer MMI, (b) SEM image of the MMI output region, (c) SEM image of the output waveguide's facet.

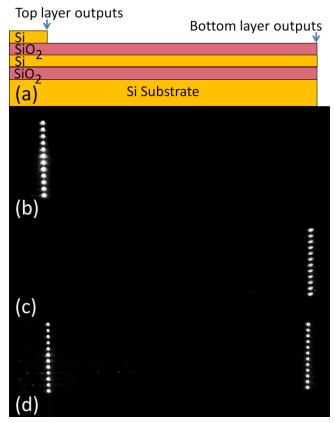

A six-axis automated aligner system with a movement precision of 50nmis utilized to couple TE polarized light at a wavelengthof 1550nm from a polarization maintaining lensed fiber (PMF) with a 2.5 $\mu$ m output mode diameter into the silicon waveguide inputs. An infrared (IR) camera connected to a variable objective lens captures the top-down, near-field images of the output facets. In order to visually resolve the 12 output spots, a waveguide fanout design is used to increase the separation of each adjacent channel to 30 $\mu$ m [Figure 3(c)]. In order tovisualize individual layer coupling in our double-layer device, we separate the outputs in the bottom layer from those in the top layer so that the two device layers terminate at two different locations as shown in Figure 4(a). Figures 4(b) and 4(c) illustrate the excitation of top and bottom layer MMI couplers, respectively. These results demonstrate selective coupling to each layer with negligible crosstalk, which in turn is due tothe 2 $\mu$ m thick BOX layer between the two silicon layers. Figure 4(d) illustrates the simultaneous excitation of top and bottom layer MMI couplers.

FIG. 4-4.(a) Schematic of separated outputs for the top and bottom layers. (b)IR top-down image of the double-layer MMI coupler with top layer excitation.(c)IR top-down image of the double-layer MMI coupler with bottom layer excitation.(d)IR top-down image of the double-layer MMI coupler with simultaneous excitation to both layers.

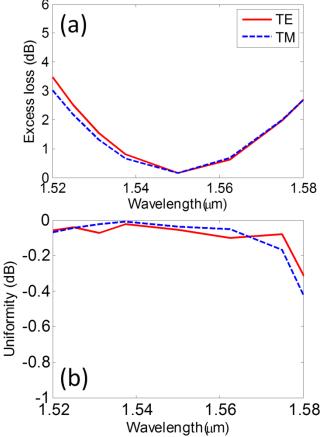

We characterize the MMI couplers on both layers by fiber scanning as described in [19]. The chip is cleaved to make measurable facets via fiber for both the top and bottom layers. A single-mode lensed fiber (SMF) is used to scan each output channel to determine the output intensity of each channel and evaluate the performance of the MMI couplers on both layers. The uniformity of an MMI coupler is defined as  $10\log(I_{\text{max}}/I_{\text{min}})$ , where  $I_{\text{max}}$  and  $I_{\text{min}}$  are the maximum and minimum intensities of the MMI output channels. The excess loss of an MMI coupler, which excludes the fiber-to-waveguide coupling loss and the waveguide propagation loss, is defined as  $-\log[(\Sigma I_m)/I_{in}]$ , where  $I_m$  is the intensity of the  $m^{th}$  output channel, and  $I_{in}$  is the output intensity of a reference waveguide on the same chip with the same cross section dimensions as the MMI access waveguides. Using FIMMPROP's fully vectorial eigenmode decomposition-based complex Film Mode Matching (FMM) solver (with 60 one-dimensional (1D) modes), we calculate the variations of the MMI excess loss and uniformity for both TE and TM polarizations [Figure 5]. Polarization independent operation is expected for a bandwidth larger than 30nm.

The top layer MMI coupler has an excess loss of 0.48dB and a uniformity within 1.1dB, while the bottom layer MMI coupler has an excess loss of 2.9dB and a uniformity within 1.7dB. Since the input waveguide is multimode, the excitation of  $TE_{0n}$  and  $TE_{mn}$  (m and n are the horizontal and vertical orders of the mode, m, n>0) modes depends on the input field launching condition, and consequently contributes to the excess

loss and output non-uniformity. In our case, the input lensed fiber mode size  $(1/e^2)$  is  $2.5\mu m \times 2.5\mu m$ , and the input waveguide TE<sub>00</sub> mode size is  $2.2\mu m \times 1.1\mu m (1.6\mu m \times 1.1\mu m)$  for the bottom (top) layer. With optimized input coupling conditions, input power is mostly coupled to the TE<sub>00</sub> mode. The MMI performance is most efficient for the TE<sub>00</sub> mode due to it having the highest effective modal index [19]. Under the excitation of the TE<sub>00</sub> mode of the input waveguide, TE<sub>m0</sub> modes will be excited, but TE<sub>0n</sub> modes will not be excited inside the multimode waveguide region [Figure 1(a)]. By comparing the measured MMI performance metrics of both layers to 1xN MMIs fabricated on a 230nm thick silicon nanomembrane (vertically single mode) [19], we confirm that the higher-order modes (inside the access waveguides) are suppressed with the optimized input coupling condition where most energy is coupled to the TE<sub>00</sub> mode. We also find that bottom layer silicon membrane has larger thickness variations than the top layer silicon membrane, which contributes to the differences in device performance for each layer.

FIG.4-5. Simulated MMI (a) excess loss and (b) uniformity as functions of wavelength for TE and TM polarizations.

In summary, we presentvertically integrated, two-layer, low loss, crystalline silicon membranes. We developed a DRIE recipe for fabrication of self-aligned waveguiding structures on double-bounded SOI substrates. The fabricated double-layer MMI couplers show low excess loss [0.48dB (top) and 2.9dB (bottom)] and uniform outputs [within 1.1dB (top) and 1.7dB (bottom) power fluctuation] and can be used for 1-to-many fanouts on different layers in 3D silicon PICs. This approach is a potential solution to the limited silicon real estate problem via vertical integration of integrated photonic devices, such as optical phased arrays (OPAs) [24] and intra- and inter-chip guided wave optical interconnects [25, 26], which require accurate alignment between vertically integrated photonic devices.

This research is supported by the Air Force Office of Scientific Research (AFOSR) Multi-disciplinary University Research Initiative (MURI) program through the AFOSR, contract # FA 9550-08-1-0394.

#### References

- [4-1] A. Shacham, B. G. Lee, A. Biberman, K. Bergman, and L. P. Carloni, in 15th Annual IEEE Symposium on High-Performance Interconnects, HOTI 2007, 2007, pp. 29-38.

- [4-2] A. Joshi, C. Batten, Y. Kwon, S. Beamer, I Shamim, K. Asanovic, and V. Stojanovic, in NOCS '09 Proceedings of the 2009 3rd ACM/IEEE international Symposium on Networks-on-Chip, 2009, pp. 124-133.

- [4-3] D. Guckenberger, S. Abdalla, C. Bradbury, J. Clymore, P. De Dobbelaere, D. Foltz, S. Gloeckner, M. Harrison, S. Jackson, D. Kucharski, Y. Liang, C. Lo, M. Mack, G. Masini, A. Mekis, A. Narasimha, M. Peterson, T. Pinguet, J. Redman, S. Sahni, B. Welch, K. Yokoyama, and Y. Shuhuan, in 2010 36th European Conference and Exhibition on Optical Communication (ECOC), 2010, pp. 1-6.

- [4-4] B. Analui, D. Guckenberger, D. Kucharski, and A. Narasimha, Journal of Solid-State Circuits41(12), 2945-2955 (2006).

- [4-5] A. Narasimha, B. Analui, E. Balmater, A. Clark, T. Gal, D. Guckenberger, S. Gutierrez, M. Harrison, R. Koumans, D. Kucharski, Y. Liang, A. Mekis, S. Mirsaidi, M. Peterson, T. Pham, T. Pinguet, V. Sadagopan, T. J. Sleboda, D. Song, Y. Wang, B. Welch, J. Witzens, S. Abdalla, S. Gloeckner, and P. De Dobbelaere, in Optical Fiber Communication Conference and Exposition and The National Fiber Optic Engineers Conference, OSA 2008, paper OMK7.

- [4-6] M. Hochberg and T. Baehr-Jones, Nature Photonics 4, 492 494 (2010).

- [4-7] M. K. Smit, in 21st Annual Meeting of the IEEE Lasers and Electro-Optics Society, LEOS 2008, 2008, pp. 51-52.

- [4-8] M. K. Smit, in Photonics in Switching, OSA 2010, paper PTuA1.

- [4-9] J. A. Kash, in Photonics in Switching, 2007, pp. 55-56.

- [4-10] K. Preston, B. Schmidt, and M. Lipson, Opt. Express 15, 17283-17290 (2007).

- [4-11] J. S. Orcutt, A. Khilo, M. A. Popovic, C. W. Holzwarth, B. Moss, H. Li, M. S. Dahlem, T. D. Bonifield, F. X. Kaertner, E. P. Ippen, J. L. Hoyt, R. J. Ram, and V. Stojanovic, in Conference on Lasers and Electro-Optics, 2008 and 2008 Conference on Quantum Electronics and Laser Science, CLEO/QELS 2008, 2008, pp. 1-2.

- [4-12] S. Zhu, Q. Fang, M. B. Yu, G. Q. Lo, and D. L. Kwong, Opt. Express 17, 20891-20899 (2009).

- [4-13] L. Liao, D. R. Lim, A. M. Agarwal, X. Duan, K. K. Lee, and L. C. Kimerling, J. Electron. Mater. 29, 1380-1386 (2000).

- [4-14] S. Selvaraja, M. Schaekers, W. Bogaerts, D. V. Thourhout, and R. Baets, in Proceedings of 11th IEEE/LEOS Benelux Annual Workshop, IEEE/LEOS, 2007, pp. 19-20.

- [4-15] Q. Fang, J. F. Song, S. H. Tao, M. B. Yu, G. Q. Lo, and D. L. Kwong, Opt. Express 16, 6425-6432 (2008).

- [4-16] T. Tsuchizawa, K. Yamada, H. Fukuda, T. Watanabe, S. Uchyama, and S. Itabashi, Jpn. J. Appl. Phys. 45, 6658-6662 (2006).

- [4-17] M. Gnan, S.Thoms, D. S. Macintyre, R. M. De La Rue, and M. Sorel, Electron. Lett. 44, 115-116 (2008).

- [4-18] K. Preston and M. Lipson, in Conference on Laser and Electro-Optics, 2007, CLEO 2007, 2007, pp. 1-2.

- [4-19] A. Hosseini, H. Subbaraman, D. N. Kwong, Y. Zhang, and R. T. Chen, Opt. Lett. 35, 2864-2866 (2010).

- [4-20] A. Hosseini, D. N. Kwong, C.-Y. Lin, B. S. Lee, and R. T. Chen, IEEE Journal of Selected Topics in Quantum Electronics 16(1), 61-69 (2010).

- [4-21] A. Brown, G. O'Neill, and S. Blackstone, Proc. SPIE 4174, 406-415 (2000).

- [4-22] F. Laermer and A. Urban, Microelectronic Engineering 67-68, 349-355 (2003).

- [4-23] I. Saraf, M. Goeckner, Brian Goodlin, Karen Kirmse, and L. Overzet, Appl. Phys. Lett. 98, 161502 (2011).

- [4-24] D. Kwong, A. Hosseini, Y. Zhang, and R. T. Chen, Appl. Phys. Lett. 99, 051104 (2011).

- [4-25] R. T. Chen, and Chulchae Choi, Synthesis Lectures on Solid State Materials and Devices (Morgan & Claypool publishers, Austin, 2007).

- [4-26] D. A. B. Miller, IEEE Journal of Selected Topics in Quantum Electronics 6(6), 1312-1317 (2000).

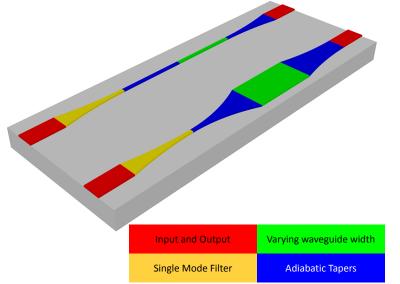

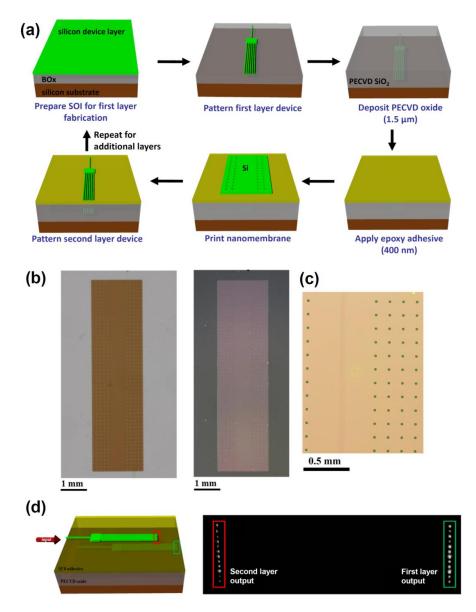

# 5.0 Double-layer Photonic devices Based on Transfer Printing of Silicon Nanomembrane for Three-dimensional Photonics

Vertical integration of multiple layers of active and passive photonic components can resolve the problem of limited real estate on a single layer silicon photonic integrated circuit (PIC) [1]. So far, deposited polysilicon has been used for photonic integration [2]. This scheme may also be used for 3D photonic integration. However, the lowest reported propagation loss is 6.45dB/cm in polycrystalline silicon waveguides with cross sectional dimensions of approximately 450 x 250nm [3], while being ~1dB/cm in crystalline silicon waveguides with the similar dimensions [4]. Additionally, polysilicon process requires high temperature crystallization anneal (~1100°C), which limit its applications in active photonic devices, such as thermal-optic devices.

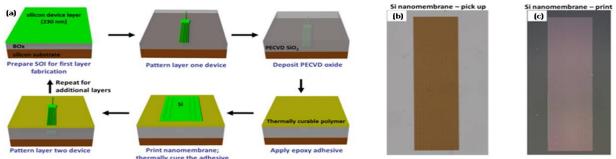

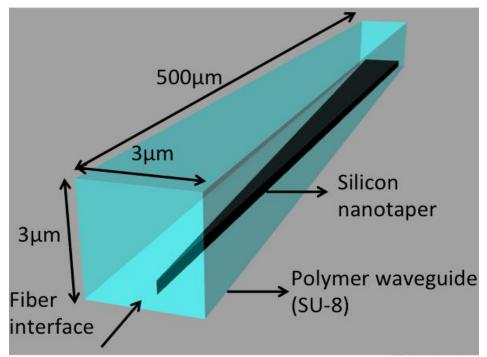

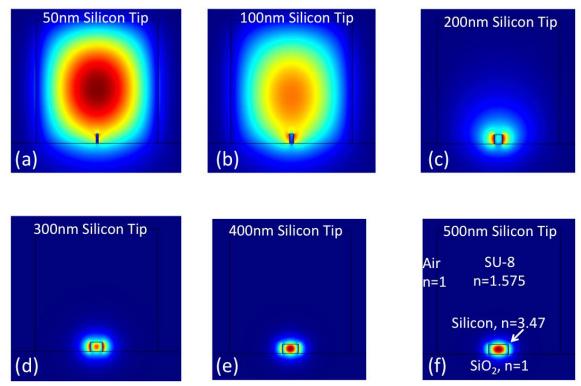

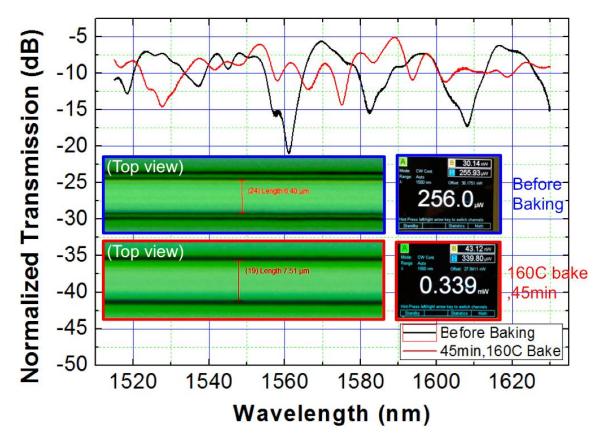

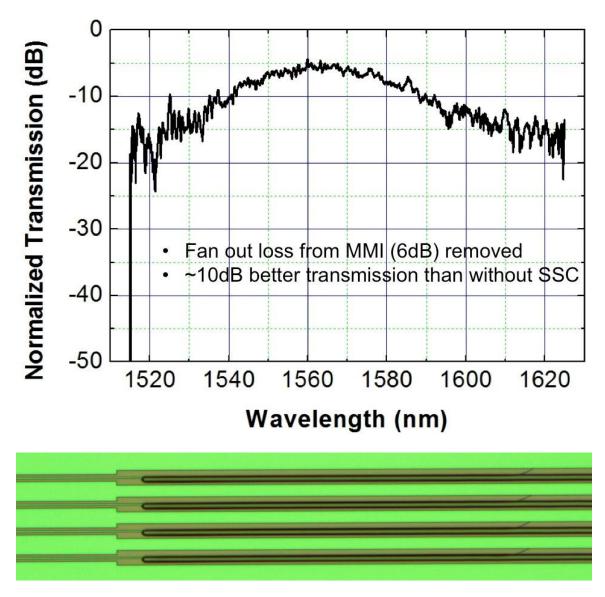

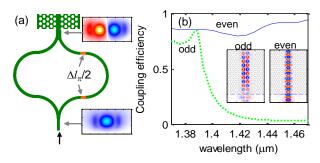

In this paper we demonstrate a novel 3D photonic integration scheme using transfer printing of silicon nanomembrane. Transfer printing based assembly techniques represent a potential transformational approach for micro/nanofabrication with far ranging fields of use. At the heart of the method is the use of printing protocols to deposit chemical or physical 'inks' in the precise architectures required by devices [5]. We fabricate double-layer 1x12 multimode-interference (MMI) couplers, with bottom layer on silicon-on-insulator (SOI) device layer and top layer on transfer printed silicon nanomembrane. MMI coupler can be used for efficient on-chip splitting. The design of MMI coupler was described in [6]. We chose the multimode waveguide width, WMMI=60µm and the corresponding multimode waveguide length, LMMI=553.4µm. The input and output access waveguide width was Ww=2.6µm. At this width, the modal phase errors were greatly reduced. The output waveguides were tapered down from 2.6 to

0.5µm for singlemode operation.

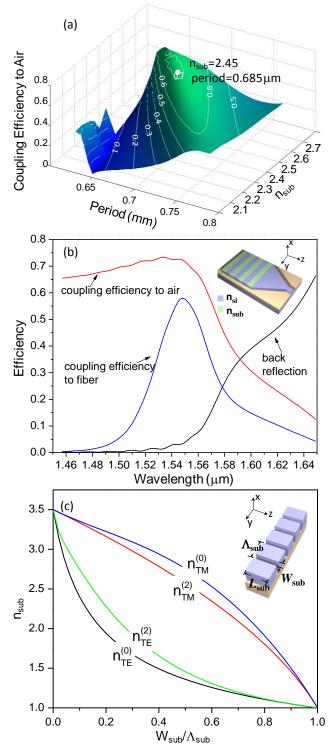

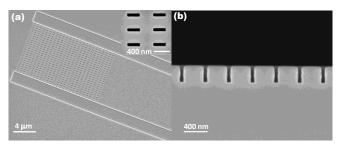

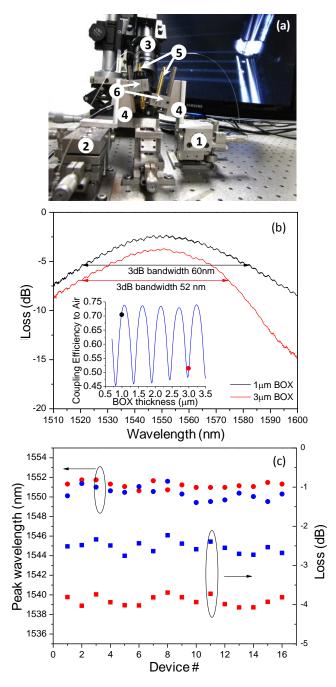

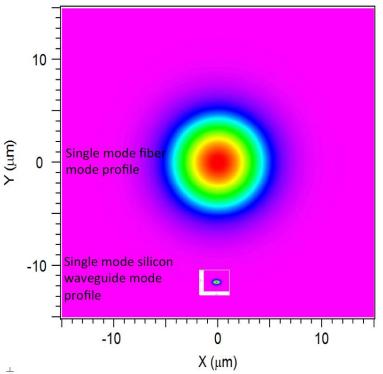

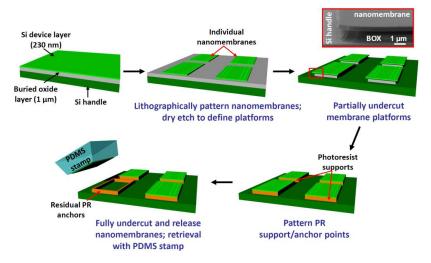

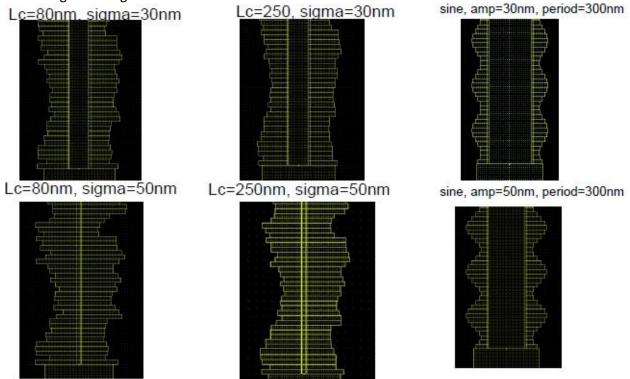

Figure 1(a) provides a schematic demonstration of the assembly process for double-layer silicon nanomembrane device platform through transfer printing and patterning steps. The device fabrication started with commercially available SOI from SOITEC with 3µm buried oxide layer (BOX) and 250nm silicon device layer. The fabrication of MMI coupler on the bottom layer using electron beam lithography (EBL) and reactive-ion-etching (RIE) was described in [7]. After etching of the silicon device layer, a silicon dioxide layer of 1.5µm was deposited using plasma-enhanced chemical vapor deposition (PECVD) as the interlayer dielectric between the bottom and top layer. Next, a thin layer (~500nm) of SU8 epoxy adhesive was spin-cast onto the silicon dioxide surface. Partial curing of the adhesive layer via heating and UV flood exposure provided a flat, firm surface for mounting additional nanomembrane as top layer.